# Extended Leslie-Singh Architecture of 1<sup>st</sup> order Delta-Sigma AD Modulator with Multi-bit DAC

Lengkhang Nengvang<sup>1,a</sup>, Shogo Katayama<sup>1,b</sup>, Jianglin Wei<sup>2,c</sup>, Lei Sha<sup>1,d</sup>, Anna Kuwana<sup>1,e</sup>, Hiroshi Tanimoto<sup>3,f</sup>, Tatsuji Matsuura<sup>4,g</sup>, Kazufumi Naganuma<sup>5,h</sup>, Kiyoshi Sasai<sup>5,i</sup>, Junichi Saito<sup>5,j</sup>, Katsuaki Morishita<sup>5,k</sup>, Haruo Kobayashi<sup>1,l,\*</sup>

<sup>1</sup>Division of Electronics and Informatics, Faculty of Science and Technology, Gunma University

1-5-1 Tenjin-cho Kiryu Gunma 376-8515, Japan

<sup>2</sup>Faculty of Intelligence Manufacturing, Yibin University, Yibin Sichuan, 64400 China

<sup>3</sup>Department of Electrical and Electronic Engineering, Kitami Institute of Technology,

Kitami, Hokkaido 090-8507, Japan

<sup>4</sup>Department of Electrical Engineering Tokyo University of Science,

Noda Chiba 278-8510, Japan

<sup>5</sup>Alps Alpine Co., Ltd., 3-31 Ake-dori, Izumi-Ku, Sendai, Miyagi 981-3280, Japan

\*Corresponding author

<sup>a</sup><t170d515@gunma-u.ac.jp>, <sup>b</sup><t15304906@gunma-u.ac.jp>, <sup>c</sup><t171d601@gunma-u.ac.jp>, <sup>d</sup><shalei201710@gmail.com>, <sup>e</sup><kuwana.anna@gunma-u.ac.jp>, <sup>f</sup><htanimot@mail.kitami-it.ac.jp> <sup>g</sup><matsuura.t@rs.tus.ac.jp>, <sup>h</sup><kazufumi.naganuma@alpsalpine.com>, <sup>i</sup><kiyoshi.sasai@alpsalpine.com> <sup>j</sup><junichi.saito@alpsalpine.com>, <sup>k</sup><katsuaki.morishita@alpsalpine.com>, <sup>l</sup><koba@gunma-u.ac.jp>

Keywords: ΔΣ ADC, multi-bit, Leslie-Singh architecture

Abstract. This paper presents extended Leslie-Singh architecture of the 1<sup>st</sup> order  $\Delta\Sigma$ AD modulator using multi-bit internal ADC and DAC. The original Leslie-Singh architecture  $\Delta\Sigma$  AD modulator uses a multi-bit ADC and a single-bit DAC inside the modulator. Here we consider an *m*-bit ADC and an *n*-bit DAC with  $m \ge n \ge 1$ . SQNDR of the modulator for various (m, n) is investigated by simulations and it is found that as *m* increases by 1, SQNDR improves by 6dB, while as *n* increases by 1, SQNDR improves by 3dB for  $m \gg n$  but it saturates for  $m \approx n$ . We have clarified that as the DAC resolution increases by 1 bit, the SQNDR improves by 3dB since the input range for the modulator stable operation is extended.

# 1. Introduction

A multi-bit  $\Delta\Sigma$  AD modulator receives much attention because the quantization noise of the ADC inside is reduced. The multi-bit ADC inside the modulator improves the signal-to-[quantization noise + distortion] ratio (SQNDR) by 6 dB for 1-bit resolution increase [1]. In many cases, a 3-bit flash is used as a multi-bit ADC because more than 3-bit flash ADC requires large hardware and power. Also, the multi-bit DAC improves the high-order modulator loop stability as well as the integrator operational amplifier swing inside the modulator is reduced, which is suitable for low power. For a continuous-time modulator, the multi-bit DAC clock jitter effects are alleviated. However, the multi-

bit DAC nonlinearity causes overall  $\Delta\Sigma$  ADC nonlinearity and hence some care such as employment of data-weighted-averaging (DWA) logic is needed [1].

Then the Leslie-Singh or Yoshitome-Uchimura  $\Delta \Sigma$  AD modulator architecture was proposed in [2, 3], where a multi-bit ADC and a single-bit DAC are used inside the modulator. It keeps the advantage of quantization noise reduction thanks to the internal multi-bit ADC, while the DAC nonlinearity problem is avoided because the single-bit DAC is inherently linear. However, it loses the multi-bit DAC advantages of higher-order loop stability and the operational amplifier swing reduction. This architecture has been used in many applications [4-10].

We proposed a charge-domain CMOS folding ADC which is fast comparable to the flash-type and it requires only *m* comparators for *m*-bit resolution [4]. A 5-bit or 6-bit charge domain CMOS folding ADC can be used inside the  $\Delta\Sigma$  AD modulator in practice, thanks to its low power and small hardware. Then we consider the generalization of the Leslie-Singh  $\Delta\Sigma$  AD modulator architecture where an *m*bit ADC and an *n*-bit DAC with  $m \ge n \ge 1$  are used. Notice that the original Leslie-Singh architecture uses a 1-bit DAC whereas our extension uses an *n*-bit DAC ( $n \ge 1$ ). *m* can be as large as 6 and in such a case, *n* is not necessarily equal to *m* for hardware and power reduction; in other words, if a flash-type ADC is employed inside the modulator, its resolution is limited up-to 3 or 4-bit due to the power and hardware restriction, but when the charge domain folding ADC is used, its resolution is extended up-to 5 or 6-bit, which motivates the present study. There are some cases that even if a 6-bit internal charge domain folding ADC is used, a 3 or 4-bit internal DAC can reduce the sampling clock jitter effects with reasonable amount of circuits; there our generalized Leslie-Singh architecture is effectively applicable.

We show here as an extension of our previous conference paper [5] that as the resolution (m-bit) of the multi-bit ADC in the extended Leslie-Singh AD modulator architecture increases by 1 bit, which is reasonable. Also, we show in simulation that as the resolution (n-bit) of the multi-bit DAC increases by 1 bit, its SQNDR increases by 3 dB, and that its reason is the extension of the stable operation input range by the DAC resolution increase.

In this paper, Section 1 describes the introduction of multi-bit  $\Delta\Sigma$  AD modulator. Section 2 presents the Leslie-Singh architecture of the 1<sup>st</sup> order  $\Delta\Sigma$  AD modulator, and Section 3 shows its simulation results. Finally, Section 4 provides the conclusion.

## 2. Extended Leslie-Singh Architecture of $1^{st}$ order $\Delta \Sigma AD$ Modulator

Leslie and Singh proposed a  $\Delta\Sigma$ AD modulator which uses a multi-bit ADC and a single bit DAC. It can reduce the quantization noise of the ADC inside the modulator and avoid nonlinearity of the DAC; this is because the single-bit DAC is inherently linear whereas the multi-bit DAC has some nonlinearities. We have mentioned a  $\Delta\Sigma$ AD modulator which uses a 6-bit or 5-bit folding ADC and a 3-bit DAC with the data-weight-averaging (DWA) algorithm logic, as the extension of the Leslie-Singh architecture and as well as an application of the charge domain folding ADC [4].

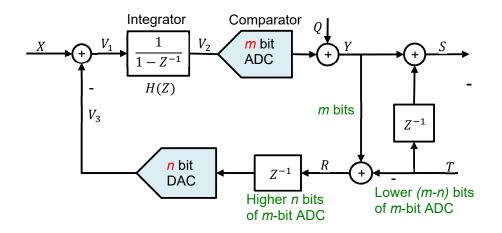

We investigate here our extended Leslie-Singh architecture of 1<sup>st</sup> order  $\Delta\Sigma$ AD modulator (Fig.1). It is composed of an analog integrator, a comparator (*m*-bit ADC) and an *n*-bit DAC ( $m \ge n \ge 1$ ). The modulator output is expressed as follow:

$$Y(Z) = V_2(Z) + Q(Z)$$

=  $\frac{1}{(1 - Z^{-1})} \{X(Z) - Z^{-1}[Y(Z) - T(Z)]\} + Q(Z)$

=  $X(Z) + Z^{-1}T(Z) + (1 - Z^{-1})Q(Z)$  (1)

Fig. 1. Extended Leslie-Singh architecture of  $1^{st}$  order  $\Delta\Sigma AD$  modulator.

Here, X(Z) is the input signal, Y(Z) is the *m*-bit ADC output, Q(Z) is the ADC quantization noise, S(Z) is the modulator output, H(Z) is the analog integrator transfer function and T(Z) is the lower (m - n) bits of *n*-bit DAC. Here, the DAC input R(Z) is the upper *n* bits of Y(Z) and the truncation signal T(Z) is expressed as the following:

$$T(Z) = Y(Z) - R(Z)$$

<sup>(2)</sup>

Then, the final output of the modulator S(Z) can be expressed as:

$$S(Z) = Y(Z) - Z^{-1}T(Z)$$

(3)

Substituting Eq. (1) into Eq. (3), the modulator output S(Z) can be written as:

$$S(Z) = X(Z) + (1 - Z^{-1})Q(Z)$$

(4)

Here, we see that the signal transfer function is 1 (STF(Z) = 1), while the noise transfer function shows that the quantization noise is the first-order noise shaped ( $NTF(Z) = 1 - Z^{-1}$ ).

#### **3. Simulation Results**

The extended Leslie-Singh architecture of  $1^{st}$  order  $\Delta\Sigma AD$  modulator in Fig.1 is simulated using MATLAB with simulation parameters in Table 1.

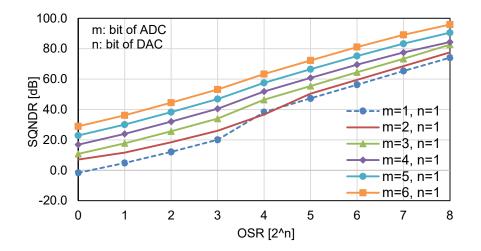

The simulation results of the over sampling ratio (OSR) versus SQNDR for the modulator with a multi-bit ADC and a single-bit DAC are shown in Fig. 2. Here, OSR and SQNDR are evaluated by the following equations:

$$OSR = \frac{f_s}{2 \cdot B} \tag{5}$$

$$SQNDR = 10 \log(\frac{Signal \ power}{\Sigma(Noise + \ distortion) \ power})$$

(6)

| ADC            | DAC            | Input Signal  | Amplitude  | Input freq.       | Data points     |

|----------------|----------------|---------------|------------|-------------------|-----------------|

| <i>m</i> [bit] | <i>n</i> [bit] | input oightai | @max value | Sampling freq.    | Data pointo     |

| 1              | 1              |               | 0.9        |                   |                 |

| 2              | 1              |               | 1.9        |                   |                 |

| 2              | 2              |               | 2.9        |                   |                 |

| 3              | 1              |               | 3.9        |                   |                 |

| 3              | 2              |               | 5.9        |                   |                 |

| 3              | 3              | Sine wave     | 6.9        | 1/2 <sup>20</sup> | 2 <sup>20</sup> |

| 4              | 1              |               | 7.9        |                   |                 |

| 4              | 2              |               | 11.9       |                   |                 |

| 4              | 3              |               | 13.9       |                   |                 |

| 4              | 4              |               | 14.8       |                   |                 |

| 5              | 1              |               | 15.9       |                   |                 |

| 5              | 2              |               | 23.7       |                   |                 |

| 5              | 3              |               | 27.8       |                   |                 |

| 5              | 4              |               | 29.7       |                   |                 |

| 6              | 1              |               | 31.9       |                   |                 |

| 6              | 2              |               | 47.5       |                   |                 |

| 6              | 3              |               | 55.7       |                   |                 |

| 6              | 4              |               | 59.6       |                   |                 |

| 6              | 5              |               | 61.9       |                   |                 |

Table 1. Simulation parameters.

The simulation results show that a multi-bit ADC improves the linearity and the quantization noise is reduced. We see in Fig 2 that a 6-bit ADC inside the modulator has the best linearity and the corresponding AD modulator achieves the high SQNDR.

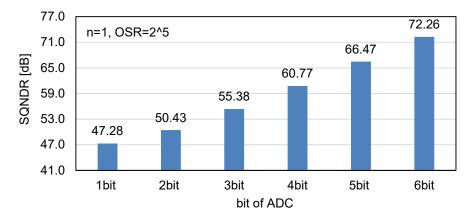

Fig. 3 shows the results of SQNDR at  $OSR = 2^5$  of the original Leslie-Singh 1<sup>st</sup> order  $\Delta \Sigma AD$  modulator with a multi-bit ADC and a single-bit DAC. We discovered that for 1-bit to 2-bit ADC the SQNDR increases by 3 [dB], whereas for 2-bit ADC to 6-bit ADC, SQNDR increase by 6 [dB] for every ADC resolution increase by 1-bit. This result is supported by the following equation:

$$SQNDR = 6.02m + 1.76 [dB]$$

(7)

Fig. 2. OSR versus SQNDR of the 1<sup>st</sup>-order Leslie-Singh modulator with various resolutions of the multi-bit ADC.

Fig. 3. SQNDR versus multi-bit ADC resolution at  $OSR = 2^5$  of the 1<sup>st</sup> order Leslie-Singh modulator.

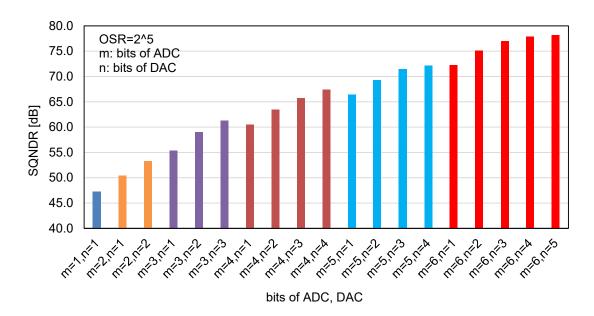

Fig. 4. SQNDR at  $OSR = 2^5$  in case of multi-bit ADC and DAC usage inside the modulator.

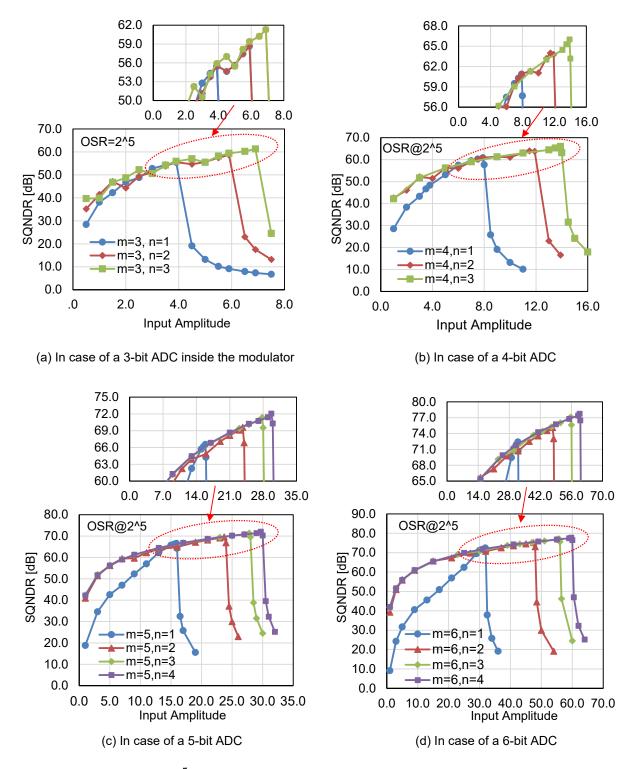

The simulation results of SQNDR at  $OSR = 2^5$  using a multi-bit DAC are shown in Fig. 4. The results in Fig. 4 show that from 1-bit DAC to 3-bit DAC, as every 1 bit increases, SQNDR is increased by 3 dB. However, more than 3-bit DAC may lead to large hardware and power with only small SQNDR improvement, and the 3-bit DAC may suffice in 6-bit ADC usage case.

We have investigated the reason why SQNDR increases by 3 dB for the DAC resolution increase by 1 bit. As Fig. 5 shows, the input amplitude for the stable operation is extended for the DAC resolution increase; the multi-bit internal DAC improves the modulator stability and hence the input range for the stable operation is widened [1]. Also the summarized simulation results of SQNDR at  $OSR = 2^5$  which uses (m, n) bits inside the modulator are shown in Table 2.

Fig. 5. SQNDR at  $OSR = 2^5$  in case of a 1-bit, 2-bit or 3-bit DAC usage inside the modulator. (a) In case of a 3-bit ADC inside the modulator. (b) In case of a 4-bit ADC. (c) In case of a 5-bit ADC. (d) In case of a 6-bit ADC.

| ADC            | DAC            | Input Signal | Amplitude  | Input freq.       | Data            | SQNDR [dB]   |

|----------------|----------------|--------------|------------|-------------------|-----------------|--------------|

| <i>m</i> [bit] | <i>n</i> [bit] | 1 5          | @max value | Sampling freq.    | points          | $@OSR = 2^5$ |

| 1              | 1              |              | 0.9        | · - ·             | •               | 47.29        |

| 2              | 1              |              | 1.9        |                   |                 | 50.40        |

| 2              | 2              |              | 2.9        |                   |                 | 53.30        |

| 3              | 1              |              | 3.9        |                   |                 | 55.40        |

| 3              | 2              |              | 5.9        |                   |                 | 59.03        |

| 3              | 3              |              | 6.9        |                   |                 | 61.30        |

| 4              | 1              | Sine wave    | 7.9        | 1/2 <sup>20</sup> | 2 <sup>20</sup> | 60.50        |

| 4              | 2              |              | 11.9       |                   |                 | 63.45        |

| 4              | 3              |              | 13.9       |                   |                 | 65.75        |

| 4              | 4              |              | 14.8       |                   |                 | 67.45        |

| 5              | 1              |              | 15.9       |                   |                 | 66.47        |

| 5              | 2              |              | 23.7       |                   |                 | 69.33        |

| 5              | 3              |              | 27.8       |                   |                 | 71.48        |

| 5              | 4              |              | 29.7       |                   |                 | 72.17        |

| 6              | 1              |              | 31.9       |                   |                 | 72.26        |

| 6              | 2              |              | 47.5       |                   |                 | 75.15        |

| 6              | 3              |              | 55.7       |                   |                 | 76.97        |

| 6              | 4              |              | 59.6       |                   |                 | 77.84        |

| 6              | 5              |              | 61.9       |                   |                 | 78.20        |

Table 2. Summarized of the simulation results.

### 4. Conclusion

The extended Leslie-Singh architecture of 1<sup>st</sup> order  $\Delta\Sigma$ AD modulator using multi-bit DAC has been investigated. Its SQNDR is analyzed and compared for various combinations of the internal ADC and DAC resolutions. The simulation results show that for 1-bit resolution increase of the multi-bit ADC, its SQNDR is increased by 6 dB. Also, we found that for 1-bit resolution increase of the multi-bit internal DAC from 1-bit to 3-bit, the SQNDR is increased by 3 dB, whereas for more than 4-bit, it saturates. Notice that the multi-bit DAC improves the modulator loop stability and the reason why the DAC resolution increase from 1-bit to 3-bit leads to SQNDR improvement is the maximum input amplitude increase with keeping stability.

Based on the study here, we consider for the multi-bit 1<sup>st</sup>-order  $\Delta\Sigma AD$  modulator design as follows: Due to the recent advancement of ADC circuit and architecture as well as LSI device and process technologies, a fast and low-power ADC can be realized, and hence the multi-bit  $\Delta\Sigma AD$  modulator with an internal ADC of 4-bit, 5-bit or 6-bit resolution can be practical; there, a 3-bit DAC inside the AD modulator would suffice (instead of a 4-bit, 5-bit or 6-bit DAC) in the viewpoint of the SQNDR using the extended Leslie-Singh architecture. In other words, usage of a 1-bit or 2-bit internal DAC sacrifices the overall ADC SQNDR there.

#### References

- [1] Understanding Delta-Sigma Data Converter, S. Pavan, R. Schreier, G. C. Temes, Second Edition, IEEE Press (New York, USA), 2017.

- [2] T. C. Leslie and B. Singh, "An Improved Sigma-delta Modulator Architecture," IEEE International Symposium on Circuit and Systems (New Orleans, LA) May 1990.

- [3] T. Yoshitome and K. Uchimura, "Quantization Noise Reduction in 1-bit Oversampling A-to-D Converter", *IEICE General Conference in Spring*, A-126, March 1988.

7

- [4] J. M. de la Rosa, R. Schreier, K. Pun, and S. Pavan, "Next-Generation Delta-Sigma Converters: Trends and Perspectives," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, Vol. 5, No. 4, pp. 484-499, 2015.

- [5] Z. Tan, H. Jiang, H. Zhang, X. Tang, H. Xin, and S. Nihtianov, "Power-Efficiency Evolution of Capacitive Sensor Interfaces," *IEEE Sensors Journal*, Vol. 21, No. 11, pp. 12457-12468, 2021.

- [6] S. Park, G.-H. Lee, and S. Cho, "A 2.92- μW Capacitance-to-Digital Converter With Differential Bondwire Accelerometer, On-Chip Air Pressure, and Humidity Sensor in 0.18-μm CMOS," *IEEE Journal of Solid-State Circuits*, Vol. 54, No. 10, pp. 2845-2856, 2019.

- [7] A. Rezapour and H. Shamsi, "Digital Noise Coupled MASH Delta-Sigma Modulator," *IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol. 66, No. 1, pp. 41-45, 2019.

- [8] C. Briseno-Vidrios, A. Edward, N. Rashidi, and J. Silva-Martinez, "A 4 Bit Continuous-Time ΣΔ Modulator With Fully Digital Quantization Noise Reduction Algorithm Employing a 7 Bit Quantizer," *IEEE Journal of Solid-State Circuits*, Vol. 51, No. 6, pp. 1398-1409, 2016.

- [9] L. He, G. Zhu, F. Long, Y. Zhang, L. Wang, F. Lin, L. Yao, and X. Jiang, "A Multibit Delta– Sigma Modulator With Double Noise-Shaped Segmentation," *IEEE Transactions on Circuits* and Systems II: Express Briefs, Vol. 62, No. 3, pp. 241-245, 2015.

- [10] J. M. de la Rosa, "Sigma-Delta Modulators: Tutorial Overview, Design Guide, and State-of-the-Art Survey," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 58, No. 1, pp. 1-21, 2011.

- [11]X. Li, T. Feng, L. Nengvang, S. Katayama, J. Wei, H. Lin, K. Naganuma, K. Sasai, J. Saito, A. Kuwana, and H. Kobayashi, "Charge Domain Folding ADC for Multi-bit ΔΣAD Modulator," *Journal of Technology and Social Science*, Vol. 6, No. 2, pp.27-37, 2022.

- [12] L. Nengvang, S. Katayama, J. Wei, L. Sha, A. Kuwana, K. Naganuma, K. Sasai, J. Saito, K. Morishita, and H. Kobayashi, "Generalized Leslie-Singh Architecture of 1st order Delta-Sigma AD Modulator with Different Resolutions of ADC and DAC," *5th International Conference on Technology and Social Science* (Kiryu, Japan) December 2021.