# Short-Time INL Testing Methodology for High-Resolution ΔΣ ADC

Jianglin Wei<sup>1,a</sup>, Nene Kushita<sup>1,b</sup>, Keno Sato<sup>2,c</sup>, Takashi Ishida<sup>2,d</sup>,

Toshiyuki Okamoto<sup>2,e</sup>, Tamotsu Ichikawa<sup>2,f</sup>, Hirotaka Arai<sup>1,g</sup>, Lei Sha<sup>1,h</sup>,

Anna Kuwana<sup>1,i</sup>, Takayuki Nakatani<sup>1,j</sup>, Kazumi Hatayama<sup>1,k</sup>,

and Haruo Kobayashi<sup>1,I,\*</sup>

<sup>1</sup>Division of Electronics and Informatics, Faculty of Science and Technology, Gunma University 1-5-1 Tenjin-cho, Kiryu, Gunma 376-8515, Japan

<sup>2</sup>ROHM Co., Ltd., 2-4-8 Shin-Yokohama, Kohoku-ku, Yokohama 222-0033, Japan \*Corresponding author

a<t192d601@gunma-u.ac.jp>, b<t181d024@gunma-u.ac.jp>, c<keno.sato@dsn.rohm.co.jp>

d<takashi.ishida@lsi.rohm.co.jp>, e<toshiyuki.okamoto@lsi.rohm.co.jp>

f<tamotsu.ichikawa@lsi.rohm.co.jp>, g<t1334006@gunma-u.ac.jp>, h<t191d031@gunma-u.ac.jp>

<sup>i</sup><kuwana.anna@gunma-u.ac.jp>, <sup>j</sup><takayuki.nakatani1017@gmail.com>

<sup>k</sup><hatayama@oak.gunma-u.ac.jp>, <sup>l</sup><koba@gunma-u.ac.jp >

Keywords: ΔΣ ADC, integral-nonlinearity, semiconductor test, polynomial modeling, FFT

Abstract. This paper describes a mass production testing methodology for integral nonlinearity (INL) of a high precision  $\Delta\Sigma$  analog-to-digital converter (ADC) in short time. We consider its INL testing by separating its analog and digital parts:  $\Delta\Sigma$  AD modulator and digital filter. The digital filter can be tested with the scan-path method. For the AD modulator part, its nonlinear curve of the DC input-output characteristics can be obtained using a DC input varying with a fine step, but it takes an enormously long time; it is not practical for mass production testing. So we consider a polynomial model of the  $\Delta\Sigma$  AD modulator input-output characteristics and estimate its coefficient values from the fundamental and harmonics power by applying a cosine input and obtaining the modulator 1-bit output power spectrum with FFT. Its INL can be estimated from the coefficients accurately when the modulator I/O characteristics is continuous. Our simulation and experimental results show that significant testing time reduction can be achieved with the proposed method.

# 1. Introduction

In recent years, Internet of Things (IoT) has attracted much attention, and the testing of IoT-related devices in short time with high quality has become more important at mass production shipping for the IoT system reliability [1-3]. This paper focuses on high-resolution low-sampling-rate  $\Delta\Sigma$  ADCs, which are widely used with sensor interface circuits, such as air flow, temperature, pressure and strain gauge sensors as well as communication circuits [4-9]. However, its integral nonlinearity (INL) testing takes extraordinary long time; for example, let us consider the case of a 7 sample-per-second (sps) 24-bit  $\Delta\Sigma$  ADC and 4 samples for each code used in its INL testing. Then its testing takes 111 days, which is not acceptable at all because the reasonable testing time is 1 second for 1 US dollar chip.

Therefore, in most cases, the INL testing for the  $\Delta\Sigma$  ADC is omitted at mass production shipping. However, recently high quality and high reliable systems are demanded. Then we have developed its 87

INL testing algorithm with drastically reduced testing time as well as keeping good testing accuracy, and here we present its algorithm as well as simulation and experimental verifications.

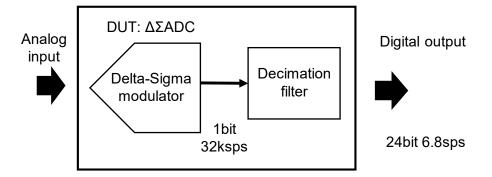

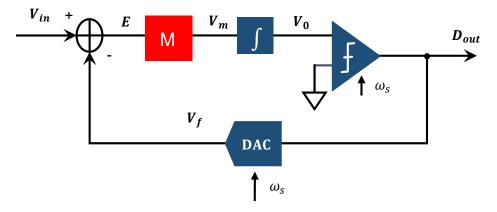

Fig.1. Configuration of a  $\Delta\Sigma$  AD converter.

## 2. ΔΣΑDC

The  $\Delta\Sigma$  AD converter is composed of a  $\Delta\Sigma$  AD modulator in the analog section and a digital filter (decimator) in the subsequent stage [4-9]. The  $\Delta\Sigma$  AD modulator performs  $\Delta\Sigma$  modulation for the analog input with oversampling, so that noise shaping for the quantization noise is realized. Then 1-bit digital data stream is provided as the modulator output, which is fed to the following digital filter for low-pass filtering and decimation; its output is the entire ADC digital output (Fig. 1).

#### 3. Proposed ΔΣ ADC Linearity Test Method

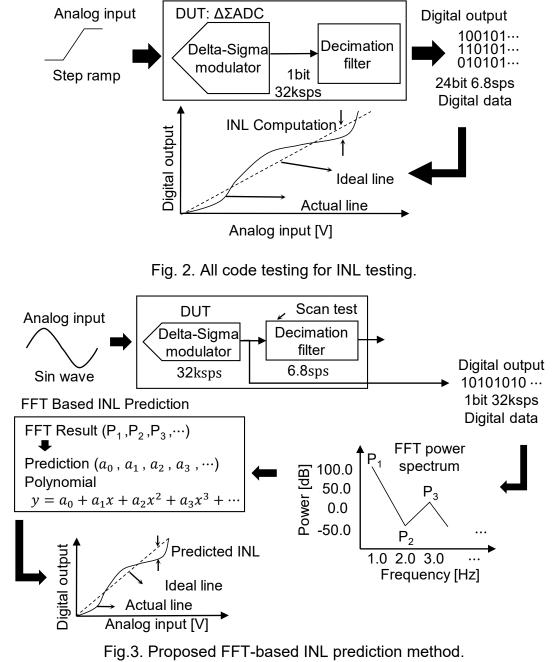

We consider a 7-sps 24-bit discrete-time  $\Delta\Sigma$ ADC for the target application. Notice that only 7 digital output data can be obtained in 1 second, and hence the direct INL testing is not acceptable at all (Fig. 2). Hence, we consider here to observe the 32-sps 1-bit data stream of the  $\Delta\Sigma$ AD modulator for the INL testing. Notice also that the INL of the overall  $\Delta\Sigma$ ADC is determined only by the  $\Delta\Sigma$ AD modulator, and the digital filter does not affect the overall ADC INL if it is well-designed and functional (i.e., without any catastrophic faults). Then we propose the following INL testing method (Fig. 3):

(1) Separate the AD modulator and the digital filter parts, and test them individually.

(2) The digital filter part is tested by the scan path method whether there are fatal faults. Notice that the digital filter part does not cause the overall  $\Delta\Sigma$ AD linearity deterioration unless it is faulty.

(3) The 1-bit output data stream of the  $\Delta\Sigma$ AD modulator is externally outputted through a test pin in test mode (Fig. 3), and it is observed during the test. Its output rate is 32ksps, which is much faster than the digital filter (decimator) output rate (7sps).

(4) Since the  $\Delta\Sigma$  AD modulator contains an analog circuit, then even if there is not a fatal fault, its linearity may be degraded by parametric faults such as parasitic circuit components, which should be checked by the testing. It is assumed here that the input /output characteristics of the  $\Delta\Sigma$  AD modulator do not have jumps (discontinuities), which is different from pipelined ADCs and SAR ADCs (Fig. 4).

(5) We model the input/output characteristics of the  $\Delta\Sigma$  AD modulator including nonlinearity characteristics model with polynomials.

Let x(t) be an input of the modulator and y(t) be its output data stream, and then we model its input/output characteristics with the following n-th order polynomial model:

$$y(t) = a_0 + a_1 x(t) + a_2 x(t)^2 + \dots + a_n x(t)^n$$

(1)

(6) We apply a cosine wave to the modulator as follows:

$$x(t) = A\cos(\omega t) \tag{2}$$

Here, the amplitude of A is known, and the input signal frequency  $\omega$  as well as the sampling clock frequency  $\omega$ s are low so that the modulator does not show high-frequency performance degradation. Then substituting Eq. (2) into Eq. (5), the modulator 1-bit output data stream is modeled by

$$y(t) = b_0 + b_1 \cos(\omega t) + b_2 \cos(2\omega t) + \dots + b_n \cos(n\omega t)$$

(3)

Using the coefficients  $a_0, a_1, a_2, \dots, a_n$ , the coefficients  $b_0, b_1, b_2, \dots, b_n$  can be expressed as follows [10, 11]:

$$b_{0} = a_{0} + \frac{1}{2}a_{2}A^{2} + \frac{3}{2^{3}}a_{4}A^{4} + \cdots$$

$$b_{1} = a_{1}A + \frac{3}{2^{2}}a_{3}A^{3} + \frac{5}{2^{3}}a_{5}A^{5} + \cdots$$

$$b_{2} = \frac{1}{2}a_{2}A^{2} + \frac{1}{2}a_{4}A^{4} + \frac{15}{2^{5}}a_{6}A^{6} + \cdots$$

$$b_{3} = \frac{1}{2^{2}}a_{3}A^{3} + \frac{5}{2^{4}}a_{5}A^{5} + \frac{21}{2^{6}}a_{7}A^{7} + \cdots$$

$$b_{4} = \frac{1}{2^{3}}a_{4}A^{4} + \frac{1}{2^{4}}a_{6}A^{6} + \frac{7}{2^{5}}a_{8}A^{8} + \cdots$$

$$b_{5} = \frac{1}{2^{4}}a_{5}A^{5} + \frac{7}{2^{6}}a_{7}A^{7} + \frac{9}{2^{6}}a_{9}A^{9} + \cdots$$

$$\vdots$$

$$b_{n-1} = \frac{a_{n-1}}{2^{n-2}}A^{n-1}$$

$$b_{n} = \frac{a_{n}}{2^{n-1}}A^{n}$$

$$(4)$$

(7) We perform FFT to the 1-bit output data stream of the modulator and obtain  $b_0, b_1, b_2, \dots, b_n$ ; then we derive  $a_0, a_1, a_2, \dots, a_n$  from the relation in Eq. (4). Now we have the following DC input/output characteristics:

$$y(t) = a_0 + a_1 + a_2 x^2 + \dots + a_n x^n$$

(5)

(8) Finally we calculate the INL of the modulator from Eq. (5) using the end-point method or the best-straight-line method [1].

Remark: In this paper, we use the end-point method for obtain INL.

**Example:** Consider the case that the 3<sup>rd</sup>-order nonlinearity is the dominant distortion for the modulator. Then we model its input/output characteristics as follows:

$$y(t) = a_1 x(t) + a_3 x(t)^3$$

(6)

Provide to the modulator a cosine wave input x(t) whose amplitude A is known.

$$x(t) = A\cos(\omega t)$$

Then the modulator output y(t) modeled in Eq. (6) is given as follows:

$$y(t) = a_1 x(t) + a_3 x(t)^3 = \left(a_1 \cdot A + \frac{3}{4}a_3 \cdot A^3\right) \cos\left(\omega t\right) + \frac{1}{4}a_3 \cdot A^3 \cos(3\omega t)$$

(7)

89

We perform FFT to y(t) and obtain its power spectrum. Then its fundamental spectrum power is given as follows:

$$b_1 = a_1 \cdot A + \frac{3}{4}a_3 \cdot A^3 \tag{8}$$

Its third harmonic spectrum power is expressed as follows:

$$b_3 = \frac{1}{4}a_3 \cdot A^3 \tag{9}$$

We can estimate the polynomial coefficients  $a_1$ ,  $a_3$  in Eq. (6) from  $b_1$ ,  $b_3$ , and A, using the relationship among  $a_1$ ,  $a_3$ ,  $b_1$ ,  $b_3$ , and A in Eqs. (8), (9). Now we can estimate the AD  $\Delta\Sigma$  modulator characteristics given by Eq. (6) and then calculate the overall ADC INL with the end-point method.

90

Fig. 4. Input/output characteristics of the  $\Delta\Sigma$ AD modulator without jumps.

# 4. Simulation Verification of Proposed Integral Linearity Test for $\Delta\Sigma$ AD modulator

### 4.1 Simulation Conditions

Section 4 shows simulation verifications of the proposed method in Section 3, in the following cases: (i) Discrete-time 1st-order and 2nd-order modulators.

(ii) 3rd-order and 5th-oder nonlinearities.

(iii) Several nonlinearity strength variations.

(iv) Several input cosine wave amplitudes.

(v) Several cases for the number of acquired 1-bit data stream of the modulator output.

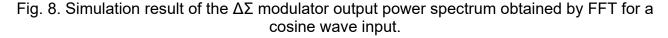

Fig. 5 shows our simulation model of the 1st-order  $\Delta\Sigma$  AD modulator with nonlinearities.

Fig.5. Simulation model of the  $1^{st}$  - order  $\Delta\Sigma$ AD modulator with nonlinearity.

Here

$$\begin{split} E(n) &= V_{in}(n) - V_f(n) \\ V_o(n) &= V_o(n-1) + V_m(n) \\ If \quad V_o(n) \geq 0, \text{then} \\ D_{out}(n+1) &= 1; \ V_f(n+1) = 1 \\ \text{Else } D_{out}(n+1) &= 0; \ V_f(n+1) = -1 \end{split}$$

The block M models the modulator nonlinearity and its nonlinearity strength can be controlled by the parameter k. Also notice that the block diagram in Fig. 5 is for system level simulation with MATLAB; in the actual circuit, the DAC output ( $V_f$ ) is  $V_{ref}$  for  $D_{out} = 1$ , or  $-V_{ref}$  for  $D_{out} = 0$ , and the range of the ADC input ( $V_{in}$ ) is from - $V_{ref}$  to  $V_{ref}$ .

In case that 3<sup>rd</sup>-order nonlinearity is dominant, we use

$$V_{\rm m}(n) = E(n) - k * E(n)^3 \ (k > 0) \tag{10}$$

In case that 5<sup>th</sup>-order nonlinearity is dominant, we use

$$V_{\rm m}(n) = E(n) - k * E(n)^5 \ (k > 0) \tag{11}$$

(12)

In subsections 4.2 - 4.6, we consider the  $3^{rd}$  - order harmonics is dominant and use Eq. (10), whereas in subsection 4.6 we consider also  $5^{th}$ -order harmonics is dominant and use Eq. (11).

#### 4. 2 DC Input-Output Characteristics with Curve Fitting

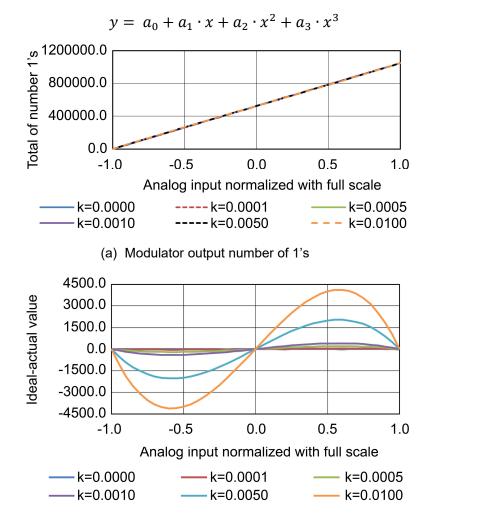

In our first simulation, we apply a DC input to the 1<sup>st</sup>-order modulator input V in in Fig. 5, from -1 to 1 with 0.05 step and obtain its input/output characteristics as a reference, even though it takes quite a large number of AD modulator samplings. The number of 1's ( $D_{out} = 1$ ) for each DC value is obtained using 2<sup>20</sup> data for a given DC input: the input DC value is changed with 0.05 step so that the total sampling number to obtain the whole input/output is enormous. The value of k representing the strength of the nonlinearity is varied as 0.0000, 0.0001, 0.0005, 0.0010, 0.0050, 0.0100, and the number of 1's at  $D_{out}$  is plotted in Fig. 6, which is the DC input/output characteristics and the INL of the modulator in Fig. 5.

The input/output characteristics in Fig. 5 are polynomial approximated by the following formula:

(b) Difference between the ideal and actual modulator output numbers of 1's.

Fig. 6. Simulation results of the DC input/output characteristics and the INL of the  $\Delta\Sigma$ AD modulator in Fig. 5 when the number of the modulator output is 2<sup>20</sup>.

Table 1 shows the values  $a_1$ ,  $a_3$  obtained from the simulation results in Fig. 6 using the curve fitting for each k,  $a_0$ , and  $a_2$ , are relatively very small due to the nonlinearity model usage of Eq. (10). So they can be ignored and are not written in Table 1. We see the followings from Table 1:

(1) As the value of k increases, the value of  $a_1$  slightly decreases.

(2) As the value of k increases, the value of a<sub>3</sub> increases.

Table.1 Estimated coefficient values in the polynomial model of the  $\Delta\Sigma$  modulator DC input/input characteristics.

<sup>93</sup>

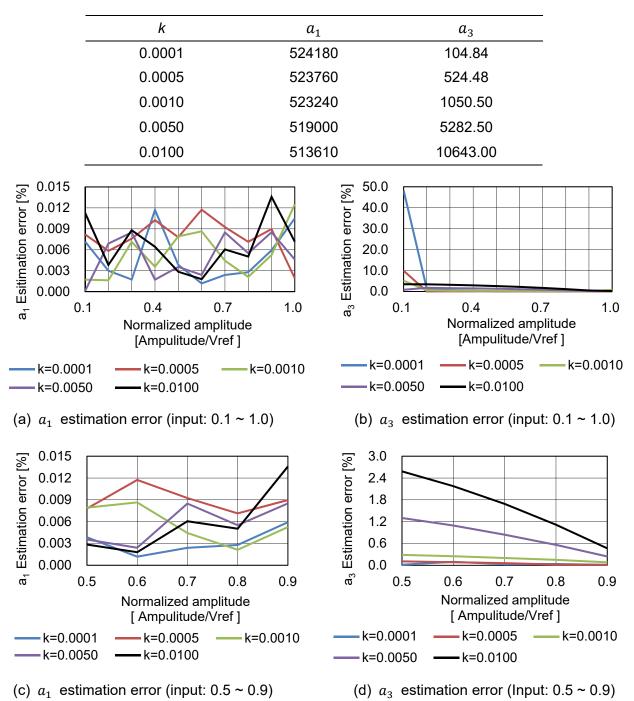

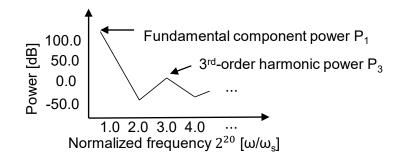

#### 4.3 Cosine Wave Input and Output Power Spectrum

Next, we consider to provide a cosine wave to the AD modulator as *V*in (Eq. (2), Fig. 3), and obtain its 1-bit output stream of  $2^{20}$  data. Then we perform FFT for the 1-bit output data stream and obtain its power spectrum; the fundamental wave power P<sub>1</sub> and the third harmonic power P<sub>3</sub> (Fig. 7). Here  $\omega_{in}/\omega_s = 1/2^{20}$ ,  $\omega_{in}$  is an input angular frequency and  $\omega_s$  is a sampling angular frequency.

As the number of the acquired modulator output data is large, the estimation accuracy for  $a_1$ ,  $a_3$  improves; we found that  $2^{20}$  is a reasonable compromise between testing time and accuracy for both the 1<sup>st</sup>-order and 2<sup>nd</sup>-order modulators.

#### 4.4 Estimation of Polynomial Coefficients with Proposed Method

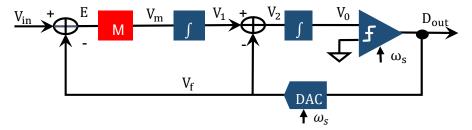

Polynomial modeling is performed for the DC input/output characteristics of the  $\Delta\Sigma$  AD modulator, based on Eq. (6). Then we estimate the values of  $a_1$ ,  $a_3$  from P<sub>1</sub> and P<sub>3</sub> obtained in Fig. 8, using Eqs. (8) and (9). Fig. 7 shows the errors of  $a_1$ ,  $a_3$  between these estimates and the ones in Table 1.

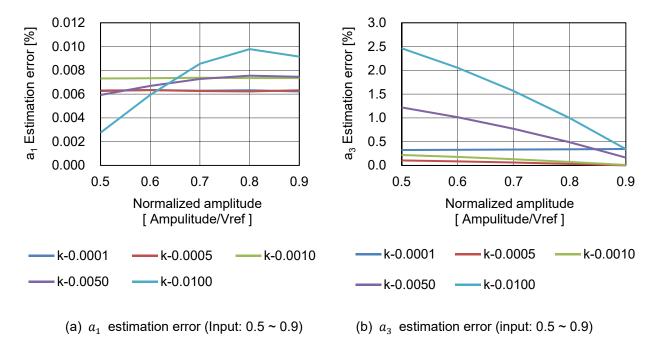

## 4.5 2<sup>nd</sup>-order Modulator Case

A  $2^{nd}$ -order modulator in Fig. 9 with  $2^{20}$  samples is also simulated with the same method. Fig. 10 shows the estimation errors of the fundamental and  $3^{rd}$  harmonics for the input with the amplitude of 0.5 to 0.9 from the  $2^{nd}$ -order modulator output power spectrum. We see the following from Fig. 8 and Fig. 10:

(1) Estimation error for  $a_1$  is small for all the input amplitude A.

(2) When the input amplitude A increases to 0.9, then the estimation error for a<sub>3</sub> is reduced. Notice that the input amplitude A is controllable during testing time.

(3) Notice that if the number of data is reduced compared to  $2^{20}$ , the estimation error becomes larger than the one as shown in Fig. 6 and Fig. 7.

(4) By comparing the 1<sup>st</sup>-order modulator with the 2<sup>nd</sup>-order modulator, the estimation errors of the both models are small. So we expect that this method is applicable for testing also high-order modulators.

Fig. 9. Simulation model of the  $2^{nd}$  -order  $\Delta\Sigma$ AD modulator with nonlinearity.

94

Here

$$E(n) = V_{in}(n) - V_{f}(n)$$

$$V_{1}(n) = V_{1}(n-1) + V_{m}(n)$$

$$V_{2}(n) = V_{1}(n) - V_{f}(n)$$

$$V_{0}(n) = V_{0}(n-1) + V_{2}(n)$$

If  $V_{0}(n) \ge 0$ , then

$$D_{out}(n+1) = 1; V_{f}(n+1) = 1$$

Else  $D_{out}(n+1) = 0; V_{f}(n+1) = -1$

The block M models the modulator nonlinearity and its nonlinearity strength can be controlled by the parameter k. In case that  $3^{rd}$ -order or  $5^{th}$  - order nonlinearity is dominant, we use Eq. (10) or Eq. (11) respectively.

Fig. 10. Estimation errors of the polynomial coefficients obtained from the 2<sup>nd</sup> - order modulator output power spectrum.

#### 4.6 Estimation of INL with Proposed Method

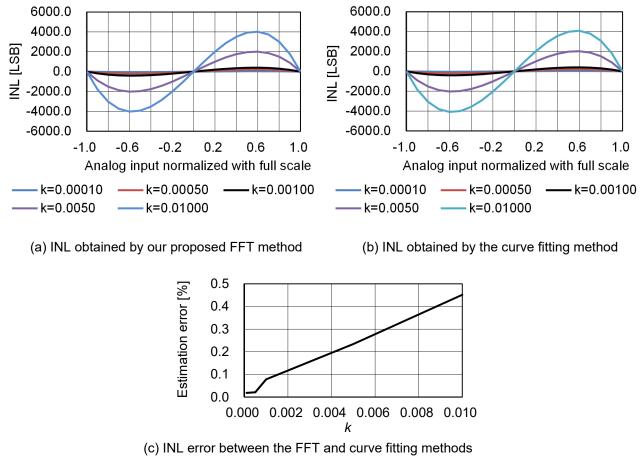

In this subsection, the INL is estimated based on our prosed FFT method and compared with the reference INL obtained by the curve fitting method using simulations. We found that the amplitude 0.9 is the best value for the accurate INL estimation, and notice that during test, the input to the  $\Delta\Sigma$ ADC under test can be controlled so that the input of 0.9  $\cos(\omega t)$  can be provided. Table 2 shows the 3<sup>rd</sup>-order and 5<sup>th</sup>-order harmonics comparison. Fig. 11 shows their comparison for the amplitude of 0.9 when the 3<sup>rd</sup>-order harmonics is dominant (Eq. (10) is used), while Fig. 12 is the one when the 5<sup>th</sup>-order harmonics is dominant (Eq. (11) is used). The vertical axes in Fig. 11 (a), (b) and Fig. 12 (a), (b) show errors of the modulator output 1's number for 2<sup>20</sup> data when 1LB is considered as 1/ 2<sup>20</sup>. We see in Fig. 11 (c), Fig. 12 (c) that estimated INL errors with our proposed method are sufficiently small.

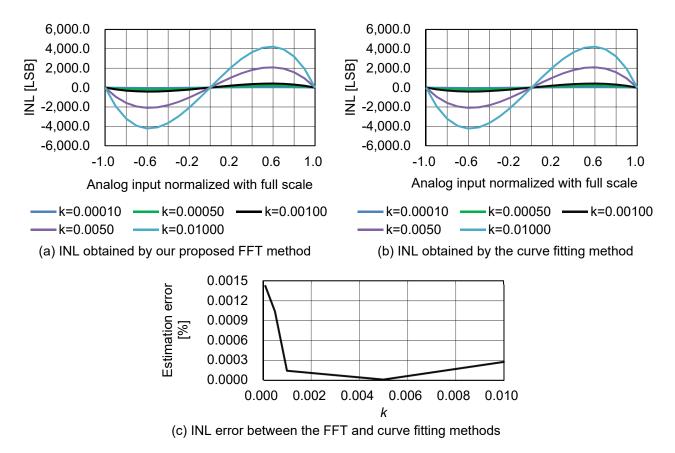

Fig. 13 shows INL errors as a function of the number of the modulator output data for the amplitude of 0.9 and k=0.0005;  $2^{14}$ ,  $2^{16}$ ,  $2^{18}$ ,  $2^{20}$  and  $2^{22}$ . We see that the number of the data is larger, the error is smaller.

95

| k      | 3 <sup>rd</sup> harmonic estimation error [%] | 5 <sup>th</sup> harmonic estimation error [%] |

|--------|-----------------------------------------------|-----------------------------------------------|

| 0.0001 | 0.0187                                        | 0.1421                                        |

| 0.0005 | 0.0213                                        | 0.1037                                        |

| 0.0010 | 0.0784                                        | 0.0142                                        |

| 0.0050 | 0.2342                                        | 0.0092                                        |

| 0.0100 | 0.4516                                        | 0.0276                                        |

Table. 2 3<sup>rd</sup> and 5<sup>th</sup> harmonics estimation maximum error.

# 5. Experimental Verification

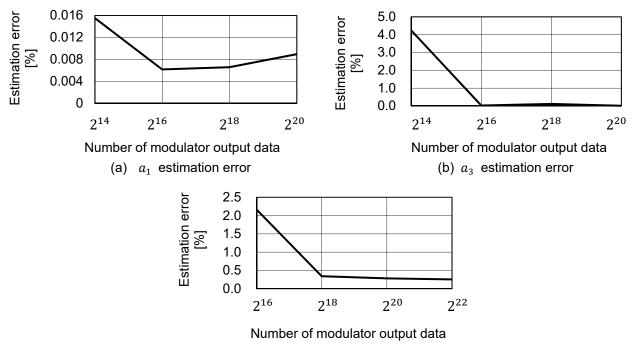

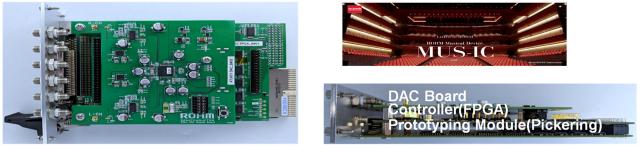

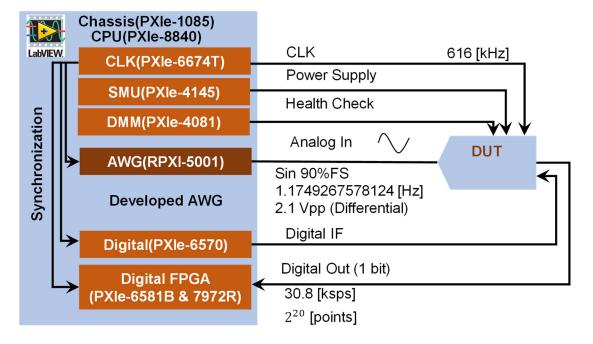

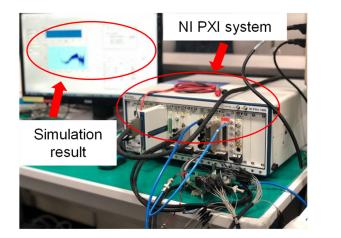

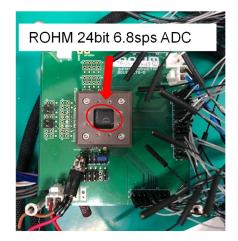

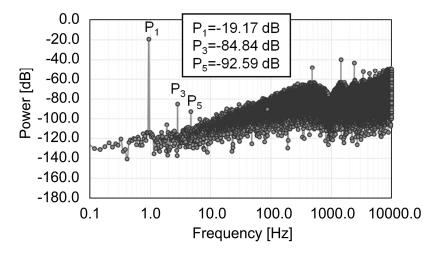

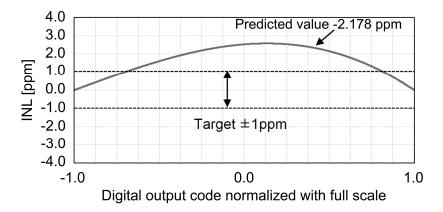

We have performed experiments with a real  $\Delta\Sigma$  ADC chip using the proposed algorithm. Our target INL test accuracy is within  $\pm$  1ppm, so that requirements for the input signal source are that THD < -120dB and SN > 130dB and synchronization between the signal source and the DUT (Device Under Test) of the  $\Delta\Sigma$ ADC in Fig. 14. Then we have developed a precise arbitrary waveform generator (AWG) whose performance is shown in Fig.15. and the NI PXI system in Fig. 16. is used and test environment in Fig. 17. The modulator output FFT results are obtained in Fig. 18, and the INL prediction is shown in Fig. 19. These results show that our proposed method can estimate the INL at ppm level.

Fig. 11. INL comparison between the FFT and curve fitting methods when the 3<sup>rd</sup>-order harmonics is dominant.

96

Fig. 12. INL comparison between the FFT and curve fitting methods when the 5<sup>th</sup> - order harmonics is dominant.

(c)  $a_5$  estimation error

Fig.13. Number of the modulator output data and estimation errors for a<sub>1</sub>, a<sub>3</sub>, a<sub>5</sub> with the proposed FFT method.

97

(a) PXI compatible module

(b) ROHM 32bit audio DAC

Fig.16. Use of NI PXI system for experiment.

98

(a) PXI setup

(b) DUT board

Fig. 17. Test environment.

Fig. 18. Experimental result of the modulator output FFT.

Fig. 19. Obtained INL prediction with the proposed method.

99

#### 6. Discussions

(i) Integral nonlinearity test time estimation:

Suppose that the  $\Delta\Sigma$ AD modulator operates with 32ksps and the required number of data for INL test is 2<sup>20</sup>. Then the required testing time is 32 seconds. If 32 chips are tested in parallel, the equivalent test time per chip is 1 second; this test time may be acceptable for industry applications. The following are calculation equations:

a) The INL testing time with the direct method for a 7-sps 24-bit  $\Delta\Sigma$ ADC is calculated by

Test Time =

$$2^{24} * \frac{1}{7} * n$$

[sec] = 666[h] \* n Here,  $n = \frac{\text{Samples}}{\text{Code}}$

In case n=4, its testing time is 111 days.

b) On the other hand, when the proposed method is used, the testing time is given by

Test Time =

$$2^{20} * \frac{1}{32,000} = 32[sec]$$

(ii) One might claim that if the gain of the operational amplifier inside the modulator is not high enough, the input/output characteristics of the  $\Delta\Sigma$  AD modulator can have jumps and it is not continuous [4]. However, our target  $\Delta\Sigma$  ADC does not have the jumps with some circuit techniques.

(iii) For the direct INL method, a precise DC signal generator with more than 24-bit resolution is required for the modulator input. However, for the proposed method, a low distortion signal generator and a low-pass filter such as [12] are enough. Recently 32-bit  $\Delta\Sigma$  ADCs are commercially announced and there would not be a DC signal generator for their INL testing with the direct method; an ultrahigh-precision DC signal source is difficult to realize.

(iv) The proposed method can be applied for high-order modulators, continuous-time modulators and multi-bit modulators; this is under investigation.

(v) The proposed method can be considered as solving so-called an inverse problem. The modulator nonlinearity is modeled as a polynomial and its coefficients are estimated by the FFT method; the modulator INL is indirectly measured by its output power spectrum.

#### 7. Conclusion

We have proposed a short-time high-accuracy integral linearity test method/algorithm of the high-resolution low-sampling-rate  $\Delta\Sigma ADC$  for mass production. We have conducted its modeling and simulation as well as experimental verification. For the next step, we will take higher-order distortions into account, and apply the proposed method to higher-order modulators. We will also perform further experiments with real  $\Delta\Sigma ADC$  chips and verify the test time in the ATE environment.

#### References

- An Introduction to Mixed-Signal IC Test & Measurement, 2nd Edition, G. Robert, F. Taenzler, M. Burns (London, UK), 2012.

- [2] Y. Sasaki, K. Machida, R. Aoki, S. Katayama, T. Nakatani, J. Wang, K. Sato, T. Ishida, T. Okamoto, T. Ichikawa, A. Kuwana, K. Hatayama, H. Kobayashi, "Accurate and Fast Testing Technique of Operational Amplifier DC Offset Voltage in μV-order by DC-AC Conversion", *Proceedings of 3rd International Test Conference in Asia: ITC-Asia2019* (Tokyo, Japan), September 2019.

- [3] H. Kobayashi, K. Kobayashi, H. Sakayori, Y. Kimura, "ADC Standard and Testing in Japanese Industry", *Computer Standards & Interfaces, Elsevier Publishers*, Vol.23, pp.57-64, 2001.

<sup>100</sup>

- [4] Understanding Delta-Sigma Data Converters, 2nd Edition, R. Schreier, S. Pavan, G. C. Temes (New Jersey, USA), 2017.

- [5] *Sigma-Delta Converters: Practical Design Guide*, 2nd Edition, J. M. Rosa (New Jersey, USA), 2018.

- [6] J. Kojima, N. Kushita, M. Murakami, H. Kobayashi, "Linearity Enhancement Algorithms of Multibit ΔΣ DA Converter-DWA, Self-Calibration and Their Combination", *Journal of Technology and Social Science*, Vol.2, No.2, pp.15-28, 2018.

- [7] J.-L.Wei, N. Kushita, H. Kobayashi, "Limit Cycle Suppression Technique Using Random Signal In Delta-Sigma DA Modulator", *Proceedings of IEEE 14th International Conference on Solid-State and Integrated Circuit Technology: ICSICT-2018* (Qingdao, China), October-November 2018.

- [8] M. Murakami, H. Kobayashi, S. N. B. Mohyar, O. Kobayashi, T. Miki, J. Kojima, "I-Q Signal Generation Techniques for Communication IC Testing and ATE Systems", *Proceedings of IEEE International Test Conference: ITC2016* (Fort Worth, TX, USA), 2016.

- [9] Data Converters, F. Maloberti (New York, USA), 2007.

- [10] Distortion Analysis of Analog Integrated Circuits, P. Wambacq, W. Sansen (Boston, USA), 2013.

- [11] F. Abe, Y. Kobayashi, K. Sawada, K. Kato, O. Kobayashi, Haruo Kobayashi, "Low-Distortion Signal Generation for ADC Testing", *Proceedings of IEEE International Test Conference: ITC2014* (Seattle, WA, USA), 2014.

- [12] T. Komuro, S. Sobukawa, H. Sakayori, M. Kono, H. Kobayashi, "Total Harmonic Distortion Measurement System for Electronic Devices up to100MHz with Remarkable Sensitivity", *IEEE Trans. on Instrumentation and Measurement*, Vol. 56, No. 6, pp. 2360-2368, 2017.

101